科普 | 设计芯片都要用到哪些软件?

最近我分享了关于 Virtuoso 套件中的 EAD 功能,发现后台有不少朋友对这个还挺陌生的,对其他EDA工具也不太熟悉。所以呢,本篇文章做个简单整理,**重点****介绍下那些在模拟设计领域里,我们经常打交道的软件工具,顺带****也会

最近我分享了关于 Virtuoso 套件中的 EAD 功能,发现后台有不少朋友对这个还挺陌生的,对其他EDA工具也不太熟悉。所以呢,本篇文章做个简单整理,重点介绍下那些在模拟设计领域里,我们经常打交道的软件工具,顺带也会分享一些我了解到的数字端工具。****

文章部分信息来源于网络资料,我会在文章末尾列出参考的信息源链接,供大家进一步查阅参考。

目录先行👇

- 模拟设计(Design&Layout)

- 电路仿真(Simulation)

- 物理验证(Physical Verification)

- 数字设计(Front-end&Back-end)

01****模拟设计

Virtuoso套件是Cadence公司提供的模拟设计解决方案,它包括了以下几个主要工具:

- Virtuoso Schematic Editor(VSE):设计电路的起点,用于绘制和编辑电路原理图;

- Analog Design Environment Suite(ADE):一个集成开发环境,它整合了设计、仿真、验证等多个环节;

- Virtuoso Layout Suite(VLS):用于将原理图设计转化为版图设计和布局。

**Virtuoso 套件中的每个工具,都有多个不同功能层次的子版本,****以满足不同工艺节点和规模的设计需求。**比如Layout套件就划分了L\XL\GXL\EAD \EXL\MXL的不同版本(成熟工艺节点XL版本应该就够用了,先进工艺节点另说)。

其中最高级的 MXL 是新推出的Virtuoso Studio平台,它不仅包含了所有先前版本的功能,还集成了生成式 AI,以助力实现模拟设计的自动化(官方是这么介绍的,没试用也不知道真假,别说MXL了,EXL我还没机会用上😅)。

除了Cadence公司的Virtuoso套件,EDA 领域的其他两大巨头——Synopsys 和 Siemens Mentor 也提供了类似的工具并占据了一定的市场份额,分别是 Custom Compiler(通过收购SpringSoft Laker得以加强)及 Tanner 。

📌Tips

Synopsys 的 In Design 功能,它与Virtuoso Layout的 EAD 工具类似,用于版图寄生参数的提取和优化。顺便一提,新思科技(Synopsys) 在B站上有官方账号,在这里分享了 In Design 功能的视频教学。👇

(来源:https://space.bilibili.com/1087454290/video)

下方是我整理的软件汇总表,列出了这几家EDA公司的主要工具信息(Synopsys 和 Siemens 两家工具使用的不多,这里先重点介绍 Cadence 家族的产品吧🤗):

| Cadence | Synopsys | Siemens EDA (Mentor Graphics) | | --- | --- | --- | | Virtuoso Schematic Suite(VSE):

- Schematic Editor L

- Schematic EditorXL Analog Design Env. Suite(ADE):

- ADE Explorer(原ADE L/XL)

- ADE Assembler(原ADE GXL)

- ADE Verifier | Custom Compiler(CC)

- Schematic Editor | Tanner

- S-Edit

- T-Spice | | Virtuoso Layout Suite(VLS):

- Layout L/XL/GXL/EAD

- Layout EXL - ICADVM20.1

- Layout MXL - IC 23.1 | Custom Compiler(CC)- Layout Editor- ASO.ai(AI驱动) | Tanner- L-Edit |

VSE 各版本功能差异一览表

| Feature | L | XL |

|---|---|---|

| Regular Function | ✓ | ✓ |

| Constraints Manager | ||

| Circuit Prospector | ||

| HTML Publisher | ||

| SPICE to Schematic | ||

| Schematic to CPF model | ✓ |

ADE各版本功能差异一览表

| Feature | Explorer | Assembler |

|---|---|---|

| Regular Function | ✓ | ✓ |

| Sweeps and Corners | ||

| Monte Carlo | ||

| Parametric Set | ✓ | ✓ |

| Local SweepMulti-Test Editor(MTE)CalibrationWaveform ComparisonMaestro SKILL InterfaceResolving Invalid Designs | ✓ |

VSL 各版本功能差异一览表

| Feature | L | XL | GXL | EAD | EXL | MXL |

|---|---|---|---|---|---|---|

| Basic editingSKILL PcellsDRD | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ |

| SDL | ||||||

| Constraints Manager | ||||||

| Pin To Trunk | ✓ | ✓ | ✓ | ✓ | ✓ | |

| ModGens | ||||||

| Placers | ||||||

| VSR | ||||||

| FloorPlanner | ✓ | ✓ | ✓ | ✓ | ||

| RC Engine | ||||||

| EM Engine | ✓ | ✓ | ✓ | |||

| Design Intent | ||||||

| SDR | ||||||

| Concurrent Layout | ||||||

| Schematic Assistant | ||||||

| InDesign DRC | ||||||

| Auto Via | ||||||

| CurvyCore Pcells | ||||||

| Photonic Interactive | ✓ | ✓ | ||||

| Layout Reuse&Migration | ||||||

| Cross Section Viewer | ||||||

| DeviceLevel Auto Routing | ||||||

| Assembly Auto Routing | ||||||

| Multi-Fabric&Tech Support | ✓ |

02

电路仿真

电路设计完成后,需要利用仿真工具来验证电路的实际性能。**Cadence公司的Spectre Simulation Platform 和 Synopsys 公司的 PrimeSim****都是业界广泛认可的仿真工具。**两种工具各有千秋,在仿真精度、速度和集成兼容性方面都各有侧重。

**Spectre Simulation Platform 是一个多模式仿真平台,产品组合包含多个仿真器,可以适应不同类型的仿真需求。**其中:

- Spectre和Spectre APS是最基础和常用的产品,可满足大部分的仿真验证需求;

- Spectre-X和Spectre-FX仿真器采用了更高效的算法加速仿真,适用于较大规模的设计验证;

- FMC Analysis 仿真器是集成在 Virtuoso Studio 平台内,利用先进的机器学习技术来优化蒙特卡洛(Monte Carlo) 仿真过程。与原始的 MC 分析相比,对验证 3 ~ 6 sigma 良品率提供数量级的速度提升。

**PrimeSim 是 Synopsys 的仿真验证平台,集成了多款用于不同任务类型的仿真器。**其中:

- PrimeSim SPICE 是最基础和常用的产品,可满足大部分的仿真验证需求;

- PrimeSim HSPICE 具有较高的仿真精度,一般作为IP的签核标准;

- PrimeSim Pro 一般用于DRAM或Flash Memory的仿真验证;

- PrimeSim XA 属于Fast SPICE仿真器,适用于较大规模的设计验证。

| Cadence | Synopsys | Siemens EDA (Mentor Graphics) | | --- | --- | --- | | Spectre Simulation Platform:

- Spectre(Classic)

- Spectre APS(并行加速)

- Spectre X

- Spectre FX(FastSPICE)

- Spectre AMS Designer(混合)

- SpectreStatAI(FMC)analysic

- Legato Reliability Solution | PrimeSim:

- PrimeSim SPICE -PrimeSim HSPICE -PrimeSim Pro -PrimeSim XA

FineSim SPICE | Analog Fast SPICE (AFS) | | Spectre RF Option (RF): EMX - EMX2023.2 (RF) | HFSS (RF,ANSYS) | - | | Virtuoso Visualization&Analysis (VIVA) | PrimeWave:

- Custom WaveView | - |

03****物理验证

下面来看设计流程中的另一个关键环节——物理验证。

我们常接触的验证流程主要包括

- 设计规则检查(DRC)

- 版图与原理图对比检查(LVS)

- 电气规则检查(ERC)

- 后仿真寄生参数提取(LPE)

一般我们会把这些物理验证流程统称 “PV”,把用来检查物理规则的描述文件统称为 “RSF/Run-Set-File”。(当然如果你不这么称呼,那一定是你们对🙈)

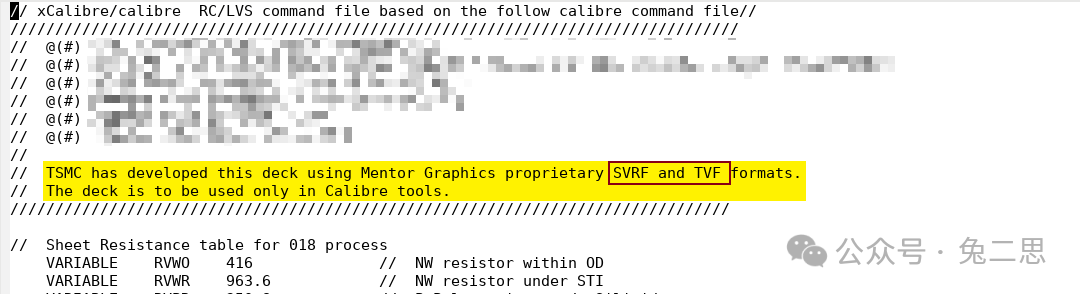

**这些检查依赖于Foundry提供的”设计规则文件”和”EDA验证工具”,验证工具只支持特定格式的RSF文件。**比如M家的 Calibre 物理验证工具,它支持的语法格式是 SVRF&TVF,C家的PVS工具支持的就有 PVL/PVTCL /iDRC/iLVS 这些格式。而且每家 Foundry 提供的SVF文件都有不同,这就是为什么在我们设计中,会有这么多不同工具的验证流程。

PS:不过话说回来,如果没有相应的工具和规则文件,验证也就无从谈起。

📌有的 Foundry 会在验证文件开头,写明用的是什么格式,想一步了解的可以去看看:

(TSMC 验证文件参考)

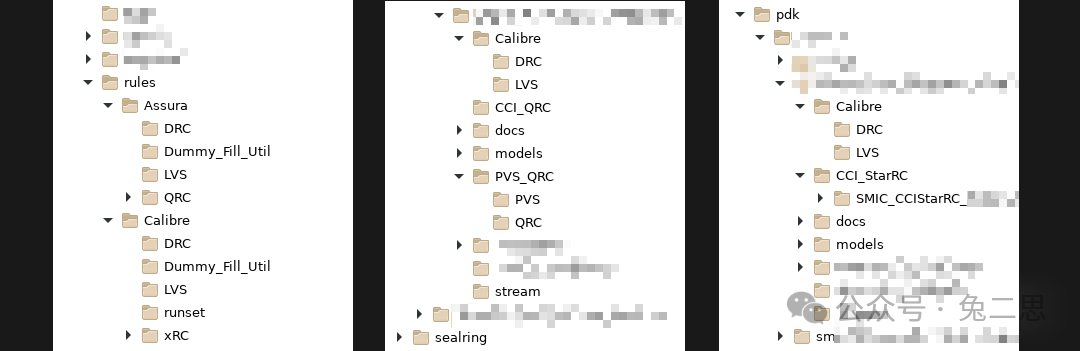

**物理验证流程中使用到的工具有很多,主要分为两部分,物理规则验证(一般包括DRC/LVS/ERC)和寄生参数提取。**前者常用的工具有Calibre,PVS/Assura,用的最多的就属 Calibre 了吧;后者常用工具有Calibre-xRC/PEX,Star-RCXT 和 Quantus/QRC。

下面来看几个 PDK 的文件夹结构,它们通常是按照验证工具的名称来命名的,尤其后仿提参阶段需要注意,工具众多叫法也各异。

(验证环节名词真的多,记得我刚学的时候也云里雾里的,真的搞不清哪个文件对应哪家的工具,就说 Foundry 厂商你们就不能统一下标准叫法的么🙃)

以为就这些工具结束了吗,还有。。。

深亚微米级开始由于工艺节点的不断缩小,设计中的制造缺陷问题越来越突出。为此 Foundry 就开始提供 DFM (Design for Manufacturing)规则检查了,你可以理解为 DFM 是更加严格的 DRC Rule,主要是为了应对因工艺制造变化对良率产生的影响。

除了DFM Rule,还有关于电源完整性和 ESD 通路仿真等验证,各家 EDA 厂商对这些检查也都有了一些相应的工具。

看下物理验证工具的汇总

| Cadence | Synopsys | Siemens EDA (Mentor Graphics) | | --- | --- | --- | | PhysicalVerificationSystems Assura Physical Verification | IC Validator(ICV) | Calibre(DRC/LVS/PERC) | | Quantus Extraction(QRC) | Star-RCXT | Calibre-xRC(PEX)成熟工艺 Calibre-xACT 先进工艺 | | Voltus-Fi(电源完整性):- L- XL Voltus-XFi | Totem(ANSYS) | - | | Pegasus DFM | - | - | | - | ESD仿真:PathFinder(ANSYS) | - |

04

数字设计

直接看汇总表,此处没有描述。。。😜

| Cadence | Synopsys | Siemens EDA | |

|---|---|---|---|

| RTL设计 | Joules Studio | ||

| Cerebrus(AI驱动) | RTL Architect | ||

| DSO.ai(AI驱动) | - | ||

| RTL综合 | GENUS-23.1 | Design Compiler(DC) | |

| Fusion Compiler | Precision RTL | ||

| Oasys-RTL | |||

| 功能仿真 | Xcelium | VCS | QuestaSimModelSim |

| 形式验证 | Conformal-24.1 | Formality | Questa |

| STA时序 | SSV-23.1(Tempus/VoltusIC) | Prime Time(PT) | Velocity |

| 波形调试 | SimVision | Verdi | Veloce RV |

| DFT | Modus-23.1 | TestMAX | Tessent |

| P&R | Innovus-23.1 | IC Compiler II(ICC2) | |

| Fusion Compiler | Aprisa | ||

| 寄生提取 | Quantus(QRC) | Star-RCXT | Calibre-xRC |

| 物理验证 | Pegasus PVS | IC Validator | Calibre |

| 电源完整性 | Voltus | RedHawk(ANSYS) | - |

05

最后

以上,希望本文能够让大家对芯片设计使用的工具有一个初步的了解。如果在介绍中存在遗漏或错误的地方,都欢迎大家在评论处留言指正。

参考资料

https://www.cadence.com/zh_CN/home/tools/custom-ic-analog-rf-design.html

https://www.synopsys.com/zh-cn/implementation-and-signoff.html

https://eda.sw.siemens.com/en-US/ic/ic-custom/

https://www.techinvestments.io/p/cadence-and-synopsys-next-winners

-点个赞再划走呗-

点击↙︎阅读原文,参与互动交流