SkillCAD与Virtuoso功能对比演示

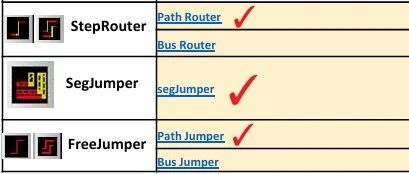

本次主要介绍**Seg Jumper,Path Jumper 和 Path Router**的功能演示。为了更加直观地展示它们的功能特点,还将和大家熟悉的 Virtuoso 进行操作对比演示。

包含此标签的文章

29 篇文章

本次主要介绍**Seg Jumper,Path Jumper 和 Path Router**的功能演示。为了更加直观地展示它们的功能特点,还将和大家熟悉的 Virtuoso 进行操作对比演示。

今天有幸参加了一场特别的专题实训——“AI辅助模拟设计”。AI与模拟设计的碰撞,不仅是两个领域的简单结合,而是模拟设计思维方式的革新。

首先,必须要强烈感谢粉丝朋友的推荐(^🙏^),让我用上了SKillCAD效率工具!我已经顺利跑了一遍安装流程,现在就把步骤记录下来分享给大家(独乐乐不如众乐乐嘛)!

在前两篇文章中,介绍了如何使用 Virtuoso EAD 工具提取寄生参数,包括:

在上篇《Part.1》文章中,我们已经掌握了如何使用 eadModelGen 程序将工艺文件转换成 eadTechFile 文件。本篇重点介绍如何设置 EAD 的一些参数,内容相对简单对于已经自行掌握的朋友可直接略过本文。

在上一篇文章中,展示了关于 EAD 工具的两个操作动图。本文开始将进一步介绍,如何使用 Layout EAD 工具来实时获取版图寄生参数的操作流程。

在芯片设计流程中,版图寄生参数的提取通常是**在LVS验证完成之后才进行**。这就意味着设计团队需要在整个设计周期的后期阶段介入,以识别并处理可能影响性能和面积的寄生效应。

收录于话题 [#Virtuoso](https://mp.weixin.qq.com/mp/appmsgalbum?__biz=MzAxMjcxNDg0NA==&action=getalbum&album_id=15688811433812

对项目而言,有时会有工艺转换的需求(process porting)即将整个项目从一个工艺移植在另一个工艺上。

「 这是Virtuoso Layout L系列的第**11**篇 」

在 IC617 中定义了一个工艺库之后,发现库的状态是灰色的,里面没有任何器件:

在某些工艺的LVS运行过程中,会弹出 “Source端网表未定义subcket” 的警告框,如下图所示:

「 这是Virtuoso Layout L系列的第**10**篇 」

「 这是Tanner L-Edit系列的第**6**篇 」

「 这是Virtuoso Layout L系列的第**9**篇 」

「 这是Tanner L-Edit系列的第**5**篇 」

「 这是Virtuoso Layout L系列的第**8**篇 」

「 这是Tanner L-Edit系列的第**4**篇 」

我们可以使用快捷键 “O” 调用VIA通孔,随后弹出Create Via选项卡:

「 这是Virtuoso Layout L系列的第**7**篇 」

「 这是Tanner L-Edit系列的第**3**篇 」

「 这是Virtuoso Layout L系列的第**6**篇 」

「 这是Tanner L-Edit系列的第**2**篇 」

「 这是Virtuoso Layout L系列的第**5**篇 」

「 这是Virtuoso Layout L系列的第**4**篇 」

本次介绍的是“L-Edit”软件,它是由Tanner 公司开发的版图设计工具(现已被Mentor公司收购)。相较于Virtuoso工具,L-Edit的优点就是它能直接在Windows系统上运行,可以很方便地在个人电脑中安装使用。

1. 快捷键介绍 2. 快捷键的几种模式 3. 快捷键的加载顺序

1. 如何启动Virtuoso软件 2. CIW窗口介绍 3. 如何定义工艺库 4. 如何创建项目库

上一篇文章,介绍了软件的启动以及库的建立。这一章讲讲在版图绘制前,首先要了解的一些基础命令。