分享 | Layout EAD实时提取版图寄生参数Part3:EMIR 检查

在前两篇文章中,介绍了如何使用 Virtuoso EAD 工具提取寄生参数,包括:

文末提供 EAD 工具演示的全套 RAK🔗

在前两篇文章中,介绍了如何使用 Virtuoso EAD 工具提取寄生参数,包括:

本篇文章主要介绍 EAD 工具中的一个关键应用 ——电迁移和电压降(EM/IR Drop)检查。

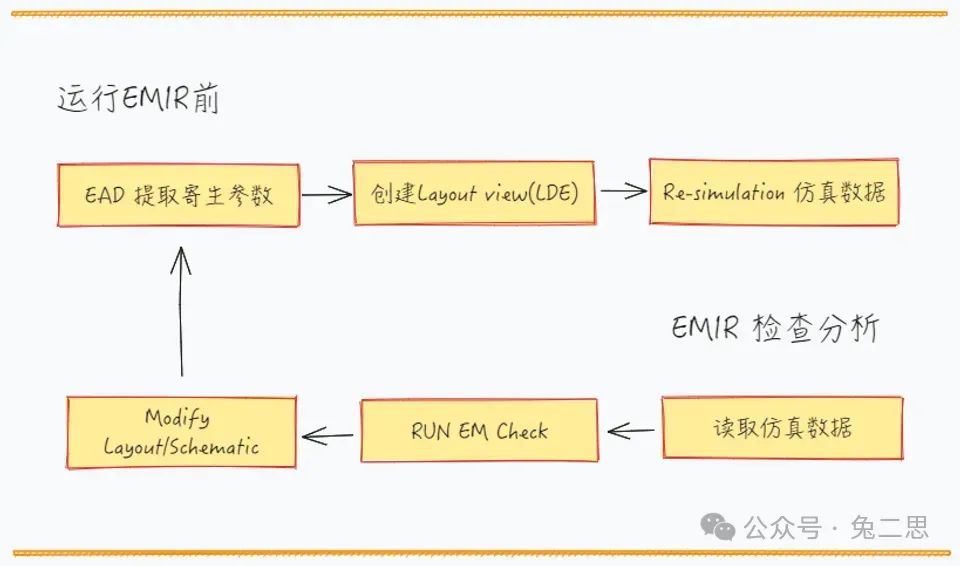

👇画了个操作流程图方便大家阅读👇

在 Virtuoso EAD 环境中,可以利用提取到的寄生参数结合 Spectre/APS 的仿真结果,进行电迁移和电压降分析。前面我们已经使用 EAD 工具,从版图中提取到了寄生信息。下一步要做的,是通过仿真工具生成电气方面的仿真数据,即****数据集(Electrical Datasets)。

EAD Browser - Electrical Dataset

📌 数据集是电流数据的一种存储形式,在 EAD 工具中它们将用作电迁移分析的输入。电流数据包括平均电流值(Average Current, Iavg)、均方根电流值(Root Mean Square Current, IRMS)和峰值电流(Peak Current, Ipeak)。

创建数据集

说在前面:由于 EMIR 检查需要用到 EAD 功能,目前只有 ADE-XL 和 ADE-Assembler 这两种仿真工具支持。

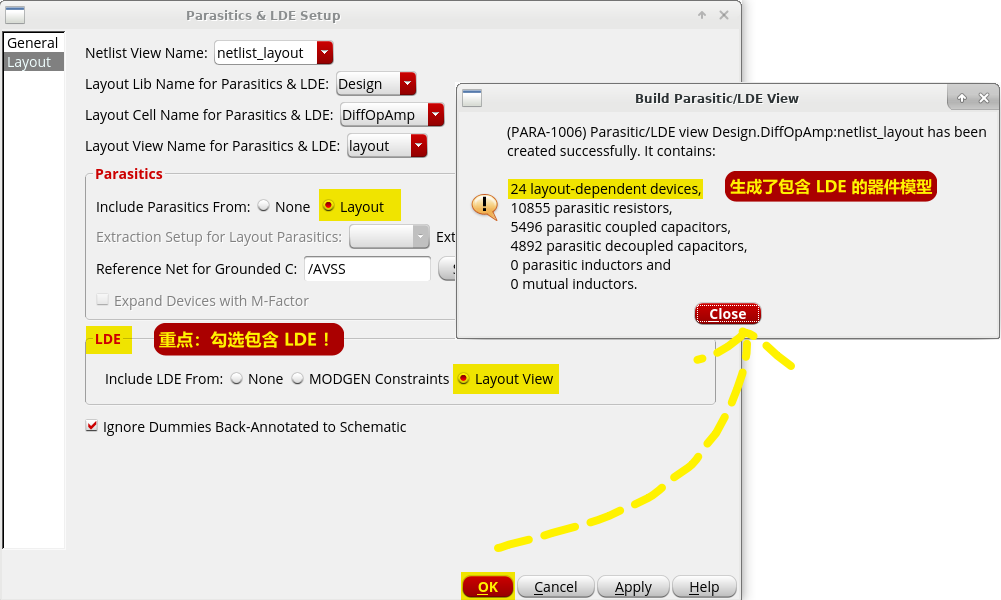

Step 1:建立寄生视图

在 EAD Browser 面板点击「Build Parasitic/LDE Netlist View」图标,设置 Parasitic & LDE Setup 选项卡,生成 netlist_layout 视图。

<<滑动查看下一张图片>>

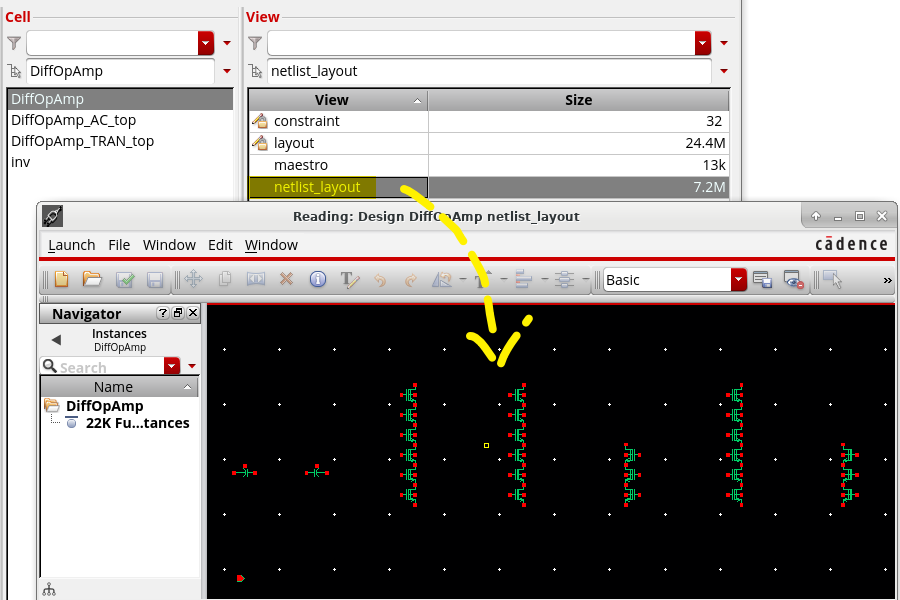

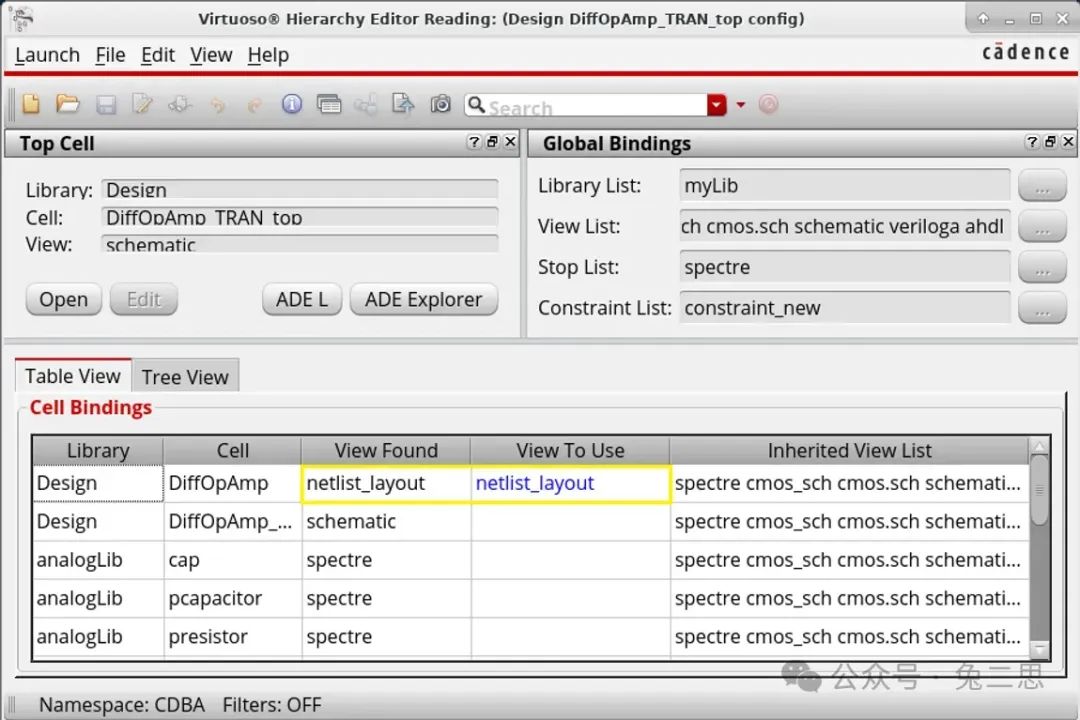

Step 2**:指定仿真的寄生参数网表**

搭建好 Testbench 电路后,打开它的 config 视图,把仿真模块的网表设为刚生成的 netlist_layout 。

设置后仿真的网表类型

🔍如何打开config视图?建议自行搜索电路仿真的操作流程。

Step 3**:设置仿真环境**

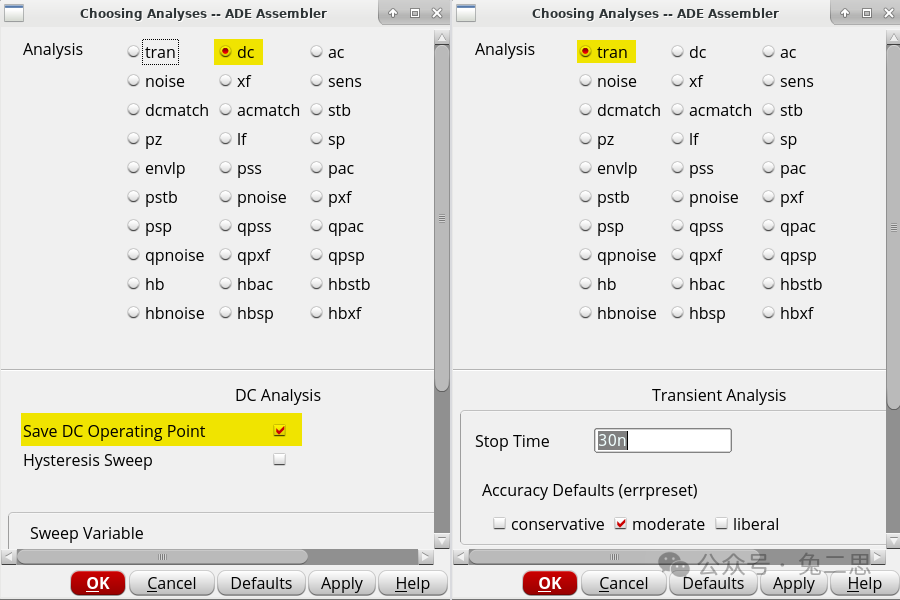

在 ADE Analysis 的设置界面中勾选「dc」和「Save DC Operating Point」,保存直流(Idc)值的仿真数据。勾选「tran」瞬态分析,用于保存瞬态电流(Iavg/IRMS/Ipeak)值的仿真数据。

Analysis 选项卡设置参考

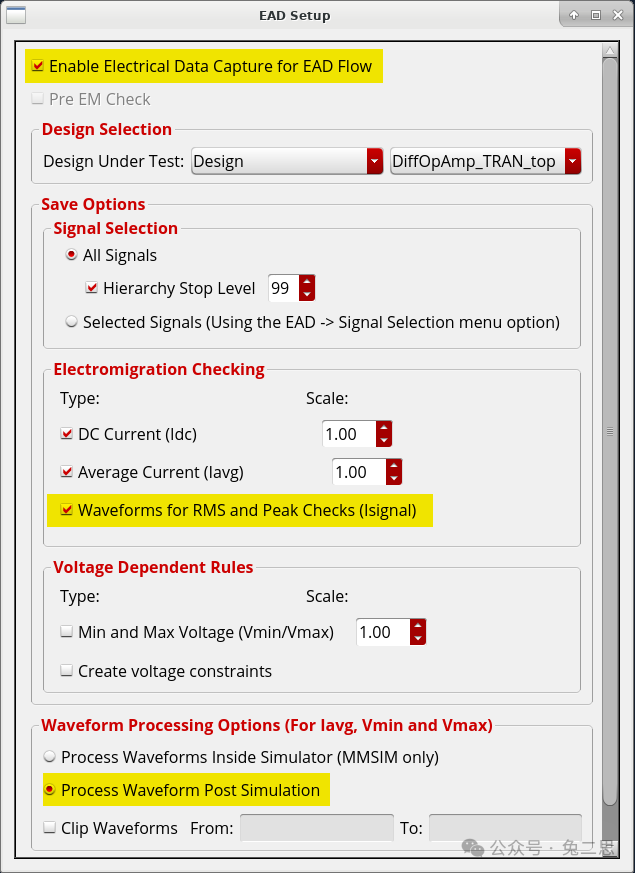

同时还需设置 ADE 中的 EAD 选项卡,点击菜单栏「EAD」-「Setup…」设置参考如下:

EAD Setup 选项卡设置参考

Step 4**:运行仿真并分析仿真结果**

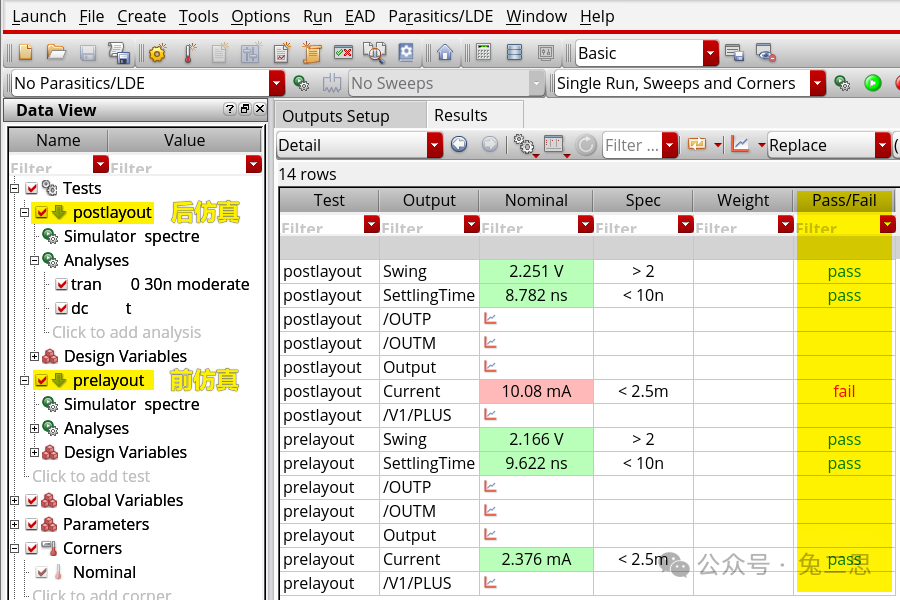

点击「Run Simulation」完成仿真后,分析寄生效应对电路性能产生的影响。附上一个 ADE-Assembler 的仿真示例图展示对比效果,其中分别列出了前/后仿真的结果,便于我们进行对比验证。

对比前/后仿真结果

Step 5**:创建数据集**

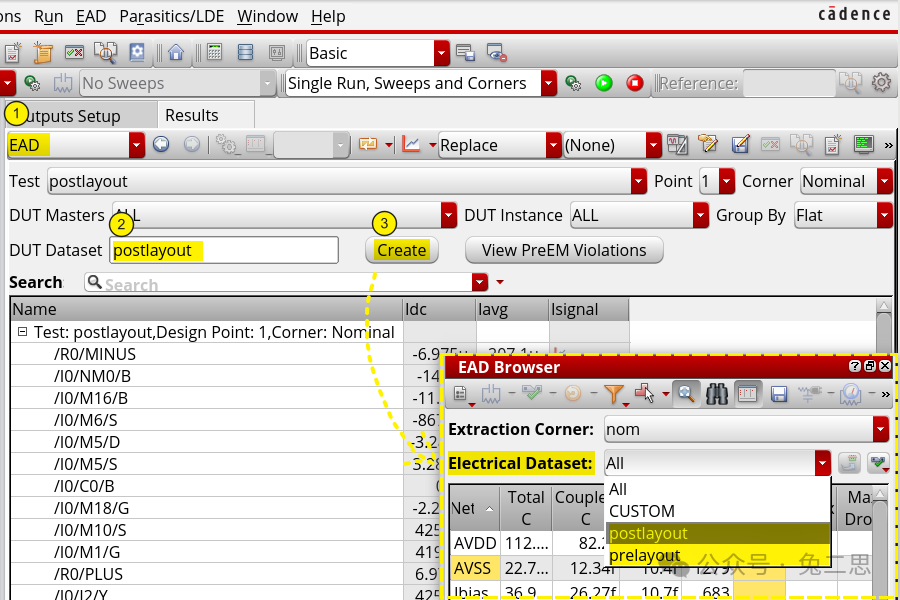

将 ADE-Assembler「Results」标签页切换成「EAD」,在 DUT Dataset 处输入名称以创建数据集。

创建Pre/Post数据集

EMIR 检查分析

有了仿真数据,我们就可以检查版图中的 EMIR 情况了。

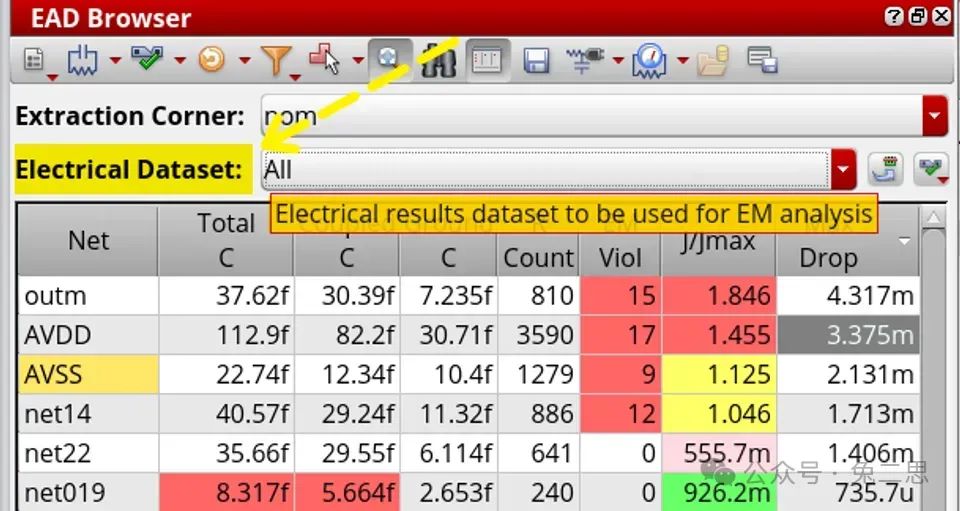

Step 6**:运行 EM 分析违规情况**

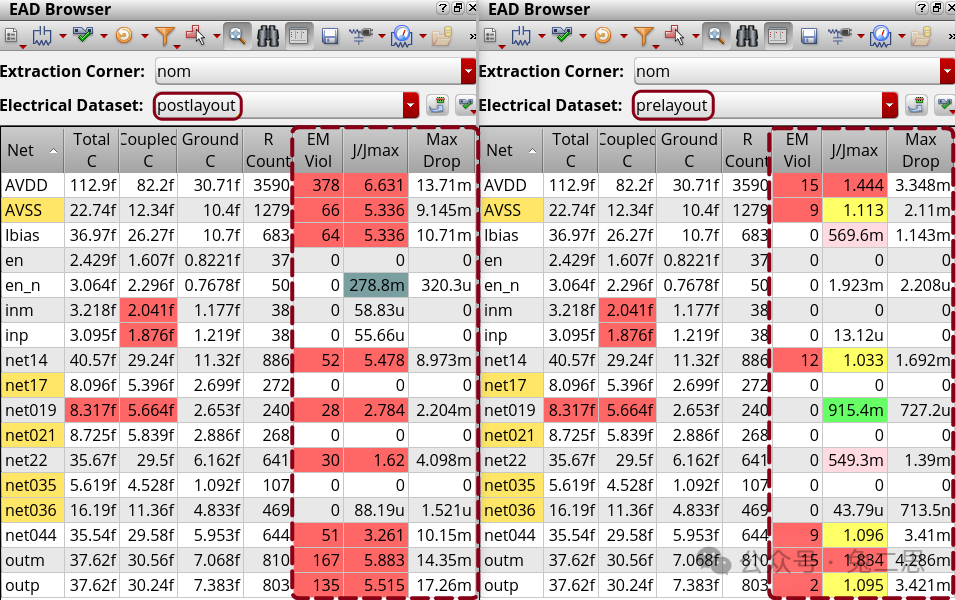

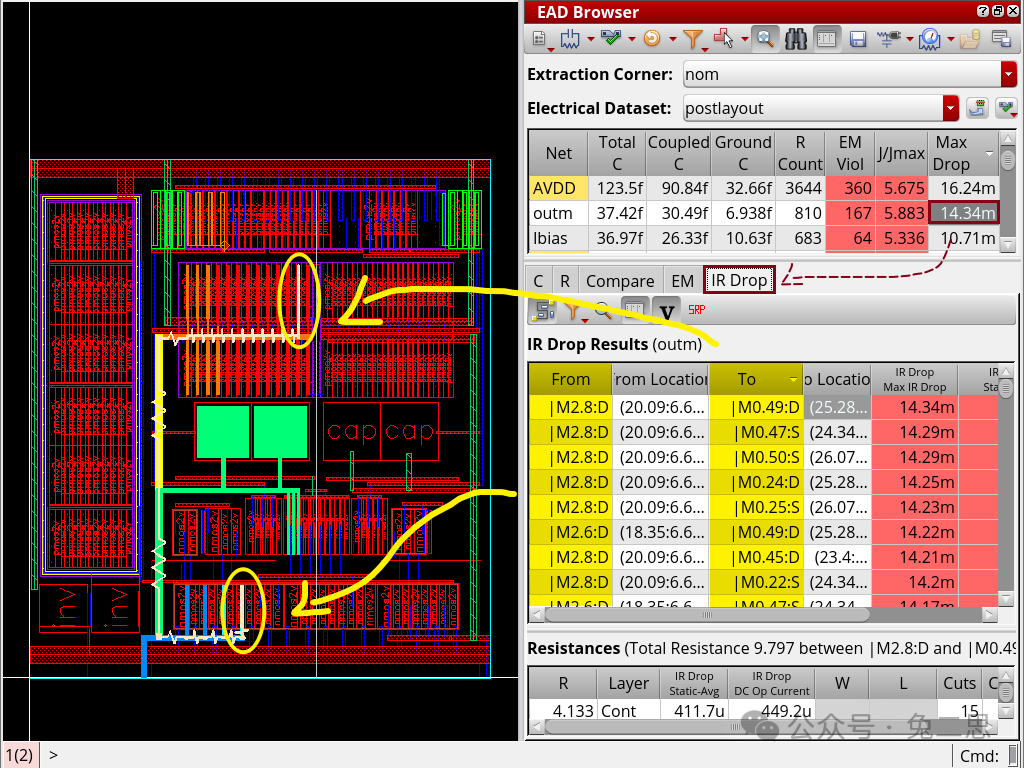

点击 EAD Browser 面板中的「Update Electrical Date …& Run EM Check」图标执行 EM 检查。运行完成后表格将新增三列数据,分别是EM Viol,J/Jmax 和 Max Drop。

EM 数据列展示

点击 EAD Toolbar Highlight 三角形图标可以直接显示 EM 热点,还可以通过选中 Net 的 EM 值,查看下方表格中更加详细的数据信息。

动图来了~

Step 7**:修复 EM 违规**

📌 进行电迁移分析时,如果发现某个 NET 的电流密度超出了安全阈值(J > Jmax),就可能需要采取措施来降低电流密度,防止电迁移问题的发生。一种常见的方法是增加导线的宽度,从而降低单位面积内的电流密度。

下面以演示案例中的信号线“outp”举例,EM 分析提示它存在两处违例,我们把金属线加宽就可以解决这个问题了。

动图来了~

鼠标悬停在 EM Results 表格中的数值处,可以显示具体的电气特性信息,其中比较有用的是 (J/Jmax*W),它是根据当前 NET 电流密度得到的建议线宽值。

通过这种方式,我们可以快速得到满足 EM 要求的金属线需要增加到多宽,确保我们的版图能够承受预期的电流密度。

Step 8**:IR drop 分析**

最后一列是 Max Drop ,可以检查点对点最大压降,对象包括电源线和信号线。“From” 指向电流起点,“To” 指向电流终点,同样可以在下方列表查看相关 net 任意两点间的压降信息。

IR Drop Results

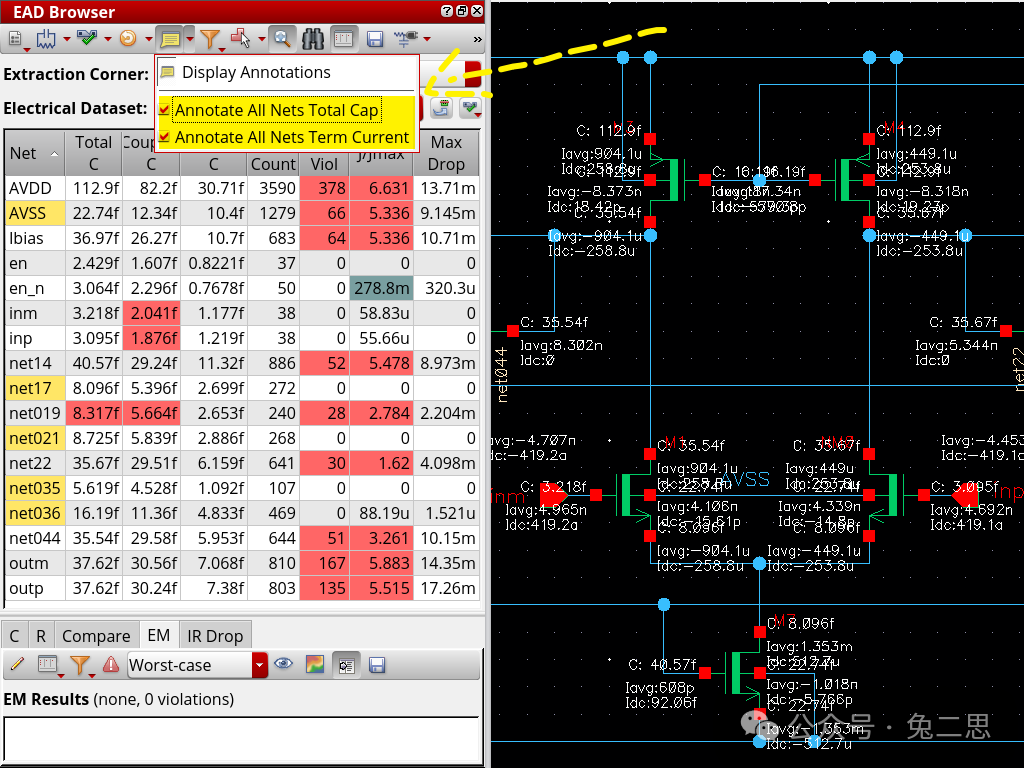

Step 9**:寄生参数反标在电路中**

回到 Schematic 窗口,菜单栏点击「Launch」-「Plugins」-「EAD」开启 Display Annotations 功能,可以显示每个器件端口的寄生电容值和 Idc,Iavg 电流值。

Display Annotations 界面展示

分享个好玩的🤗

最近使用 AI 类工具比较多,本篇文章就是借助 AI 写的,用它来梳理了写作思路。现在工作中遇到问题时也会时不时地找 AI 问问,尝试下来帮助比较大,故此分享给大家。

贴几个使用过程图,随便看看哈~

在公众号对话框回复关键词「EAD」获取下载链接

-点个赞再划走呗-

相关阅读

Layout EAD 实时提取版图寄生参数Part1:输入文件

Layout EAD 实时提取版图寄生参数Part2:参数设置

点击

阅读原文

,参与互动交流