答疑 | 如何解决“LVS验证时Source端网表未定义SUBCKT”的问题

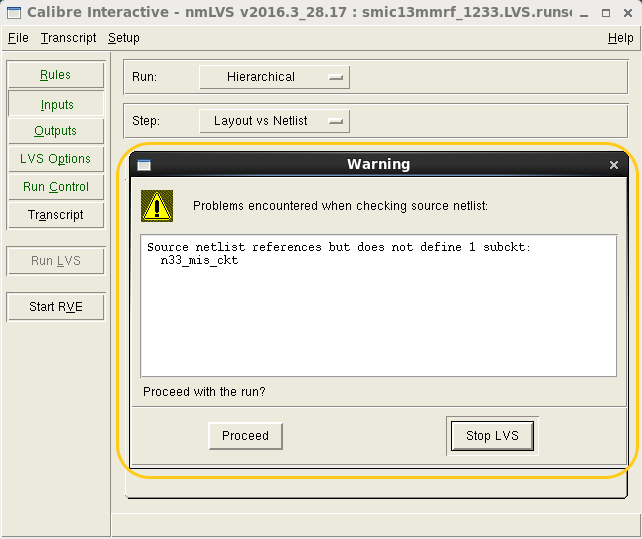

在某些工艺的LVS运行过程中,会弹出 “Source端网表未定义subcket” 的警告框,如下图所示:

问题描述

在某些工艺的LVS运行过程中,会弹出 “Source端网表未定义subcket” 的警告框,如下图所示:

⚠ Warning

⚠ Problems encountered when checking source netlist

⚠ Source netlist references but does not define 1 subckts: n33_mis_ckt

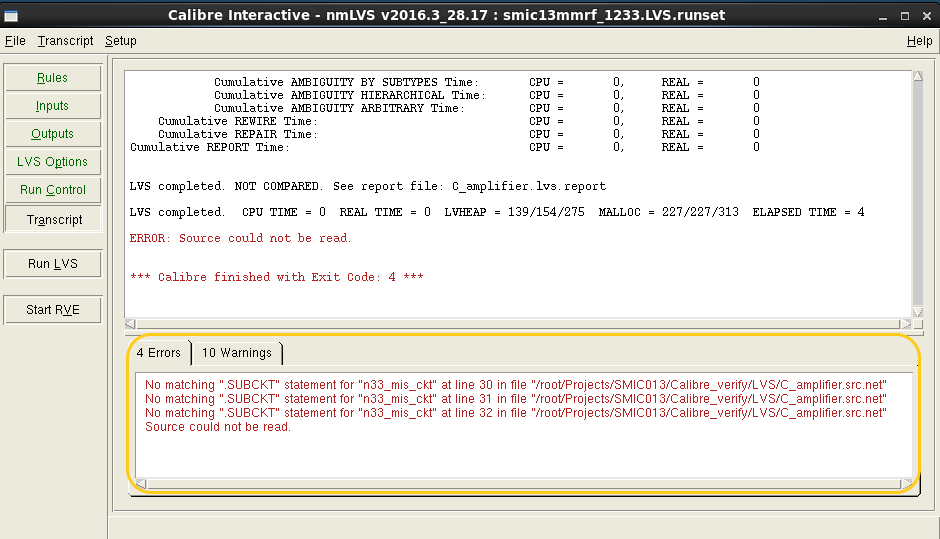

如果你点击「Proceed」继续往下,Error 提示**无法读取电路。**更多详细的报错说明如下:

解决方案

出现这个 Warning 的根本原因是,Source 端导出的CDL网表文件不完整,缺少了 “n33_mis_ckt” 器件的定义,因此存在语法错误

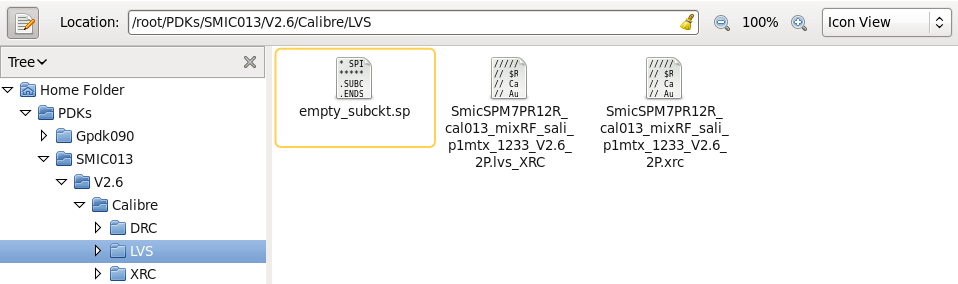

在代工厂提供的PDK中,有些工艺会在 Calibre 文件夹中,附上一份自定义器件的定义文件。这是为了符合Calibre Command的语法要求加入的文件,例如:empty_subckt.sp、3t_device.cdl

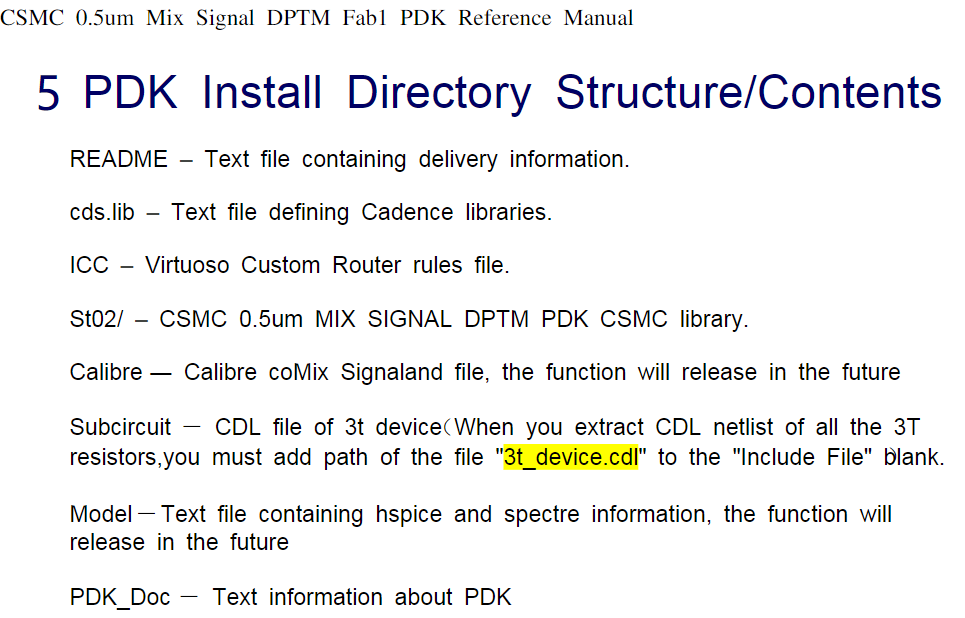

你也可以从PDK的说明文档中看到解释。这里有一份 CSMC 的PDK说明文件,如下:

其中 Subcircuit 一行解释了此文件的用途。按照要求,需将其添加到 Include File 中。也就是CDL网表应包含 “3t_device.cdl” 文件才完整。

接下来介绍添加文件的方法。

比较常见的一些做法是

1)可以使用Cadence自己的CDL导出工具,在Include选项处加上此文件

2)还可以,使用集成的Calibre工具进行 Netlist Export 的设置

上述两种方法,都可以用于添加Include文件。但是有个缺点,在每次使用时需要重新设置一遍,无法永久记住配置信息。

那么,如何自动地向CDL网表添加empty_subckt. sp****文件并记住这些设置呢?

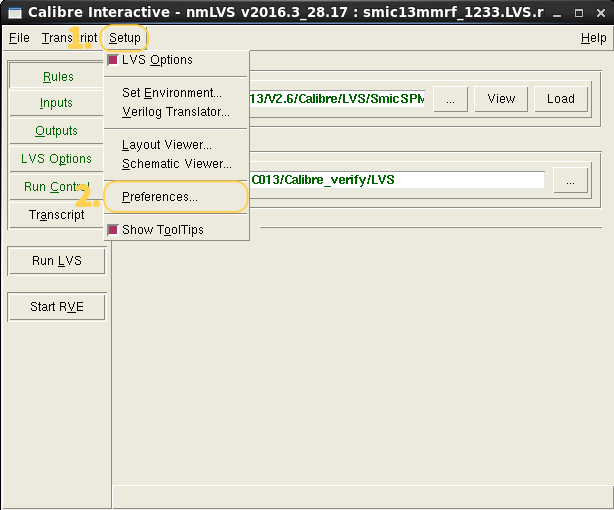

我这里选用 Calibre Interactive 交互式工具进行设置:

👉**【步骤1】**

在 Calibre Interactive 界面,标题栏处选择「Setup」-「Preferences…」

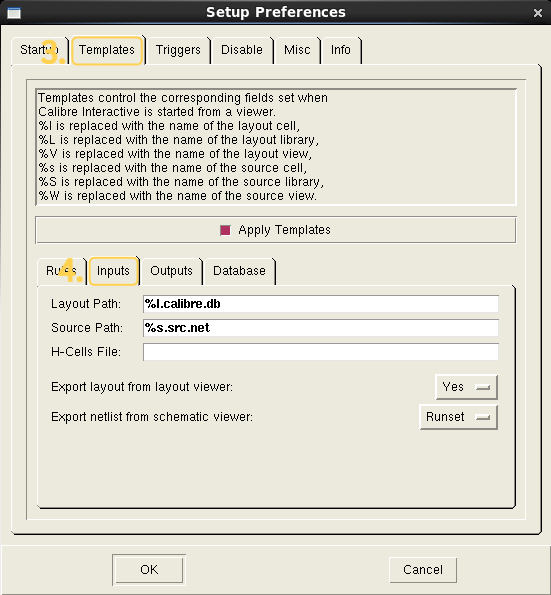

👉**【步骤2】**

弹出 “Setup Preferences” 对话框,选择子选项卡「Templates」-「Inputs」

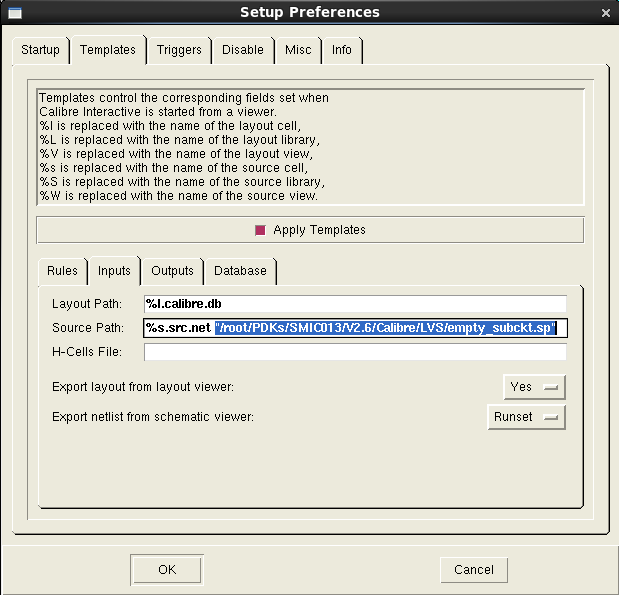

👉**【步骤3】**

在 “Source Path” 处,添加Include File的路径

直接在%s.src.net文本后面输入。如

%

s.src.net

"/root/PDKs/.../empty_subckt.sp"

其中,引号中的内容是 empty_subckt.sp 文件的路径地址,且两者中间有一个空格。

接着,你可以把设置信息保存成相应工艺专用的Runset文件,然后重新启动一遍 Calibre 运行即可。

完整的操作演示

👇👇👇

-End-

Virtuoso 实战答疑 系列

点赞鼓励一下