分享 | Layout EAD实时提取版图寄生参数Part2:参数设置

在上篇《Part.1》文章中,我们已经掌握了如何使用 eadModelGen 程序将工艺文件转换成 eadTechFile 文件。本篇重点介绍如何设置 EAD 的一些参数,内容相对简单对于已经自行掌握的朋友可直接略过本文。

在上篇《Part.1》文章中,我们已经掌握了如何使用 eadModelGen 程序将工艺文件转换成 eadTechFile 文件。本篇重点介绍如何设置 EAD 的一些参数,内容相对简单对于已经自行掌握的朋友可直接略过本文 。

。

首先,在运行 EAD 工具前必须确保

√ 已拥有 VLS EAD license;

√ 已建立 eadTechFile 文件;

√ 版图通过 Layout XL 生成,具有连接关系;

注:本流程基于 IC6.1.8 only 基础版本,不涵盖 ICADV 高级节点版本的内容

启动 EAD

打开一个版图窗口运行 EAD

- 菜单栏点击「Launch」-「Layout EAD」

- 在工具栏 Workspaces 下拉菜单中选择「EAD」

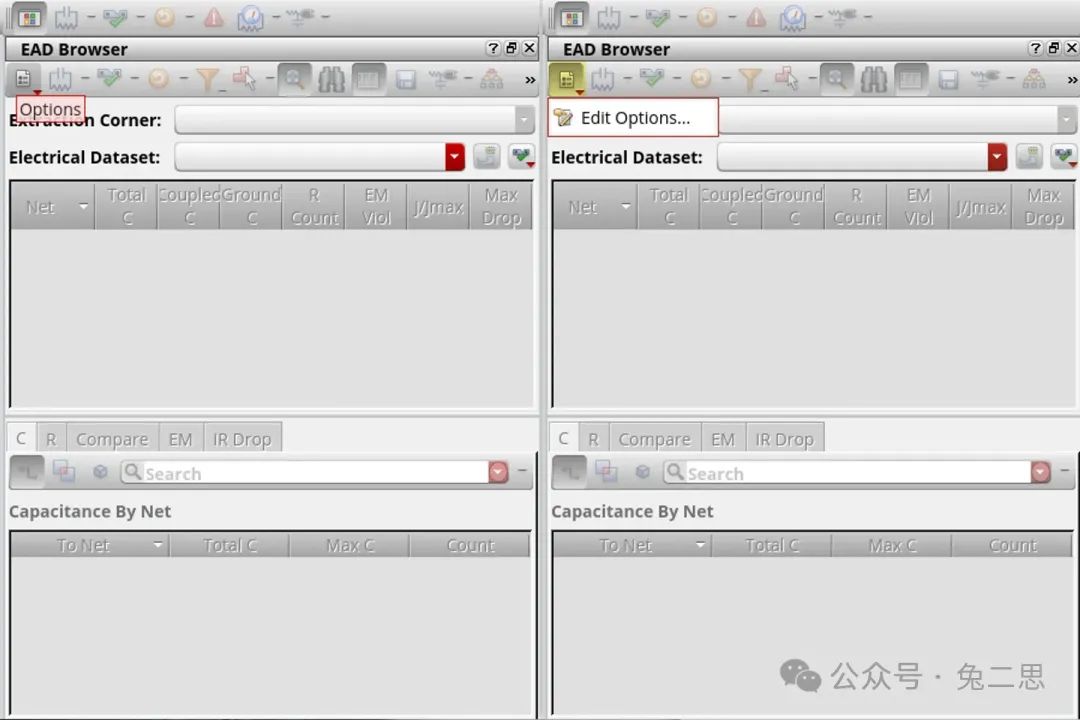

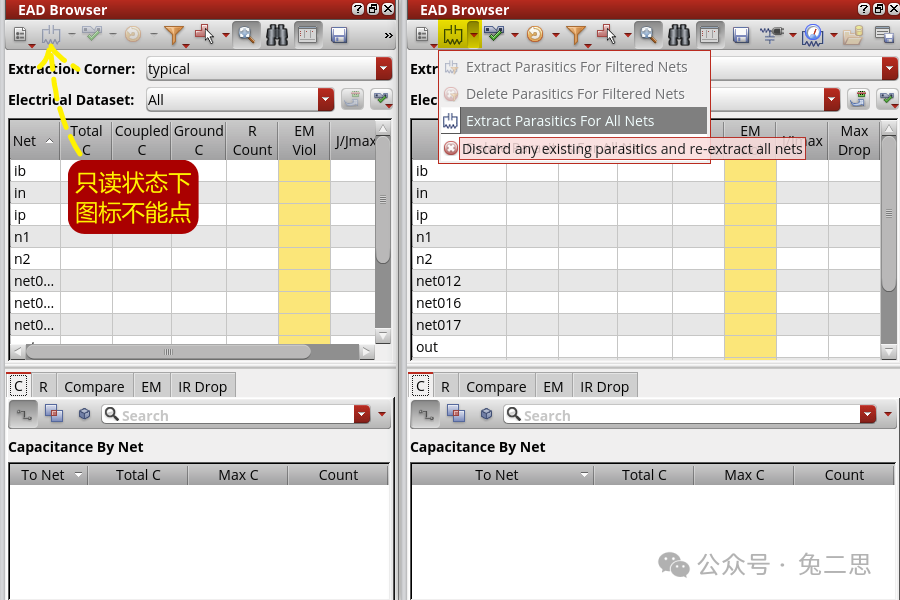

弹出的 EAD Browser 面板,初始状态下只有第一个 Options 图标可以选择,其他图标均是灰色的不可选。

EAD Browser 初始状态

配置 EAD

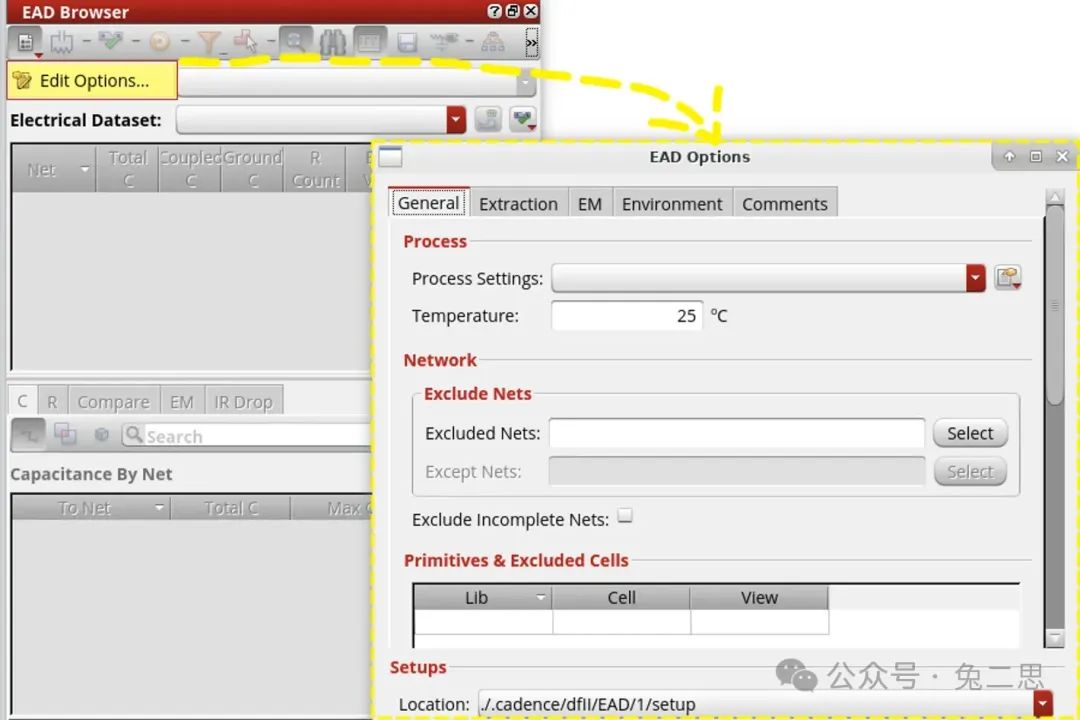

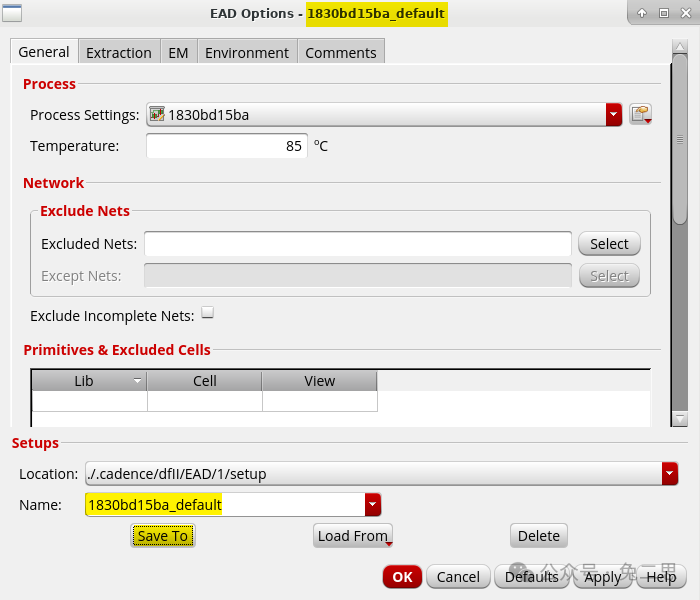

点击 Options 图标,选中「Edit Options…」之后弹出 EAD Options 选项卡,接下来的设置将在此选项卡上进行。

打开 EAD Options 选项卡

📌通过菜单栏「Options」-「Layout EAD」也可以打开 EAD Options 选项卡。

其中有多个子选项卡,主要是关于 Process 和 Setup 的参数内容。首先来看 Process 这部分的设置 —— 子选项卡 General 下方的Process。

Process 部分

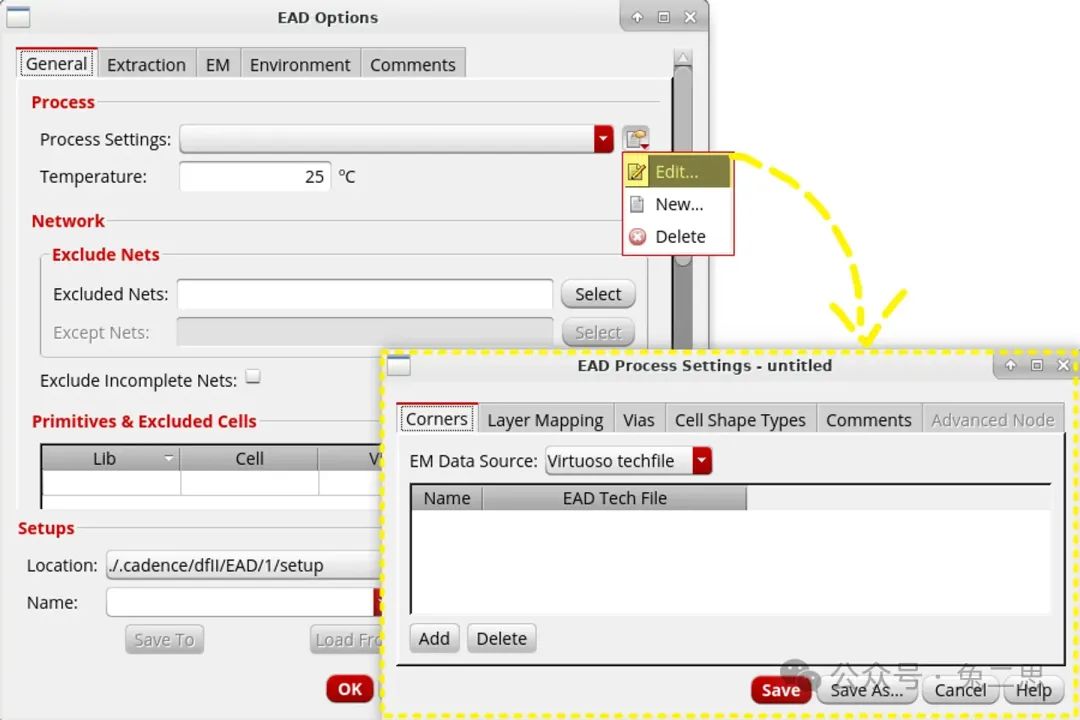

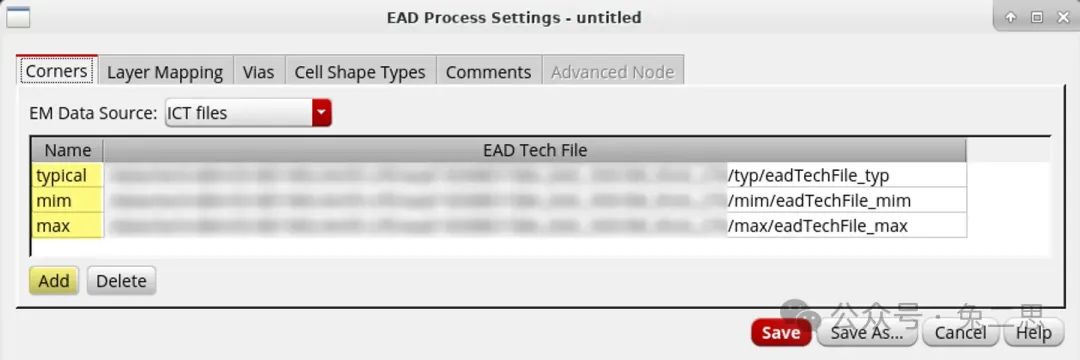

Step 1: 点击 Process Settings 右侧的图标,选择「Edit…」打开 EAD Process Settings 选项卡:

打开 EAD Process Settings 选项卡

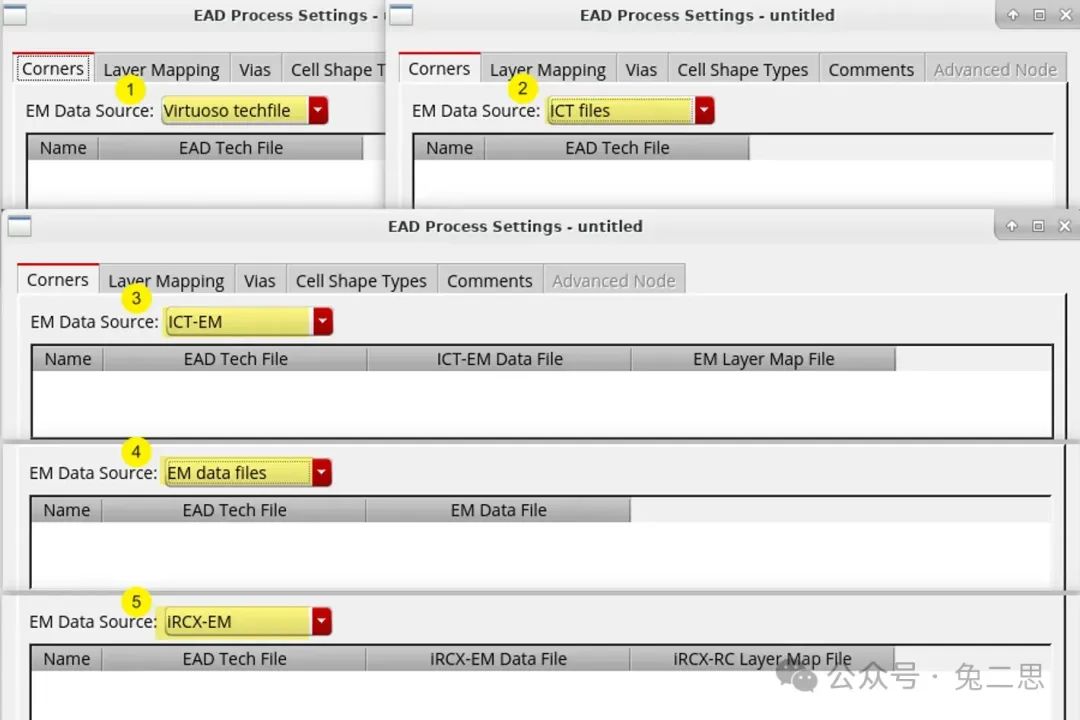

Step 2: 从 EM Data Source 下拉列表选择一个数据源。

针对含有 EM 数据的工艺文件,有多种不同的数据格式可供选择。其中 iRCX 是由 TSMC 厂商设计的一种数据格式文件。

EM 数据源列表

(找了一圈没有找到开源的 EM 数据文件这里就不举例了…)

Step 3: 在表格中填入 Corner Name 和各个数据文件的路径。

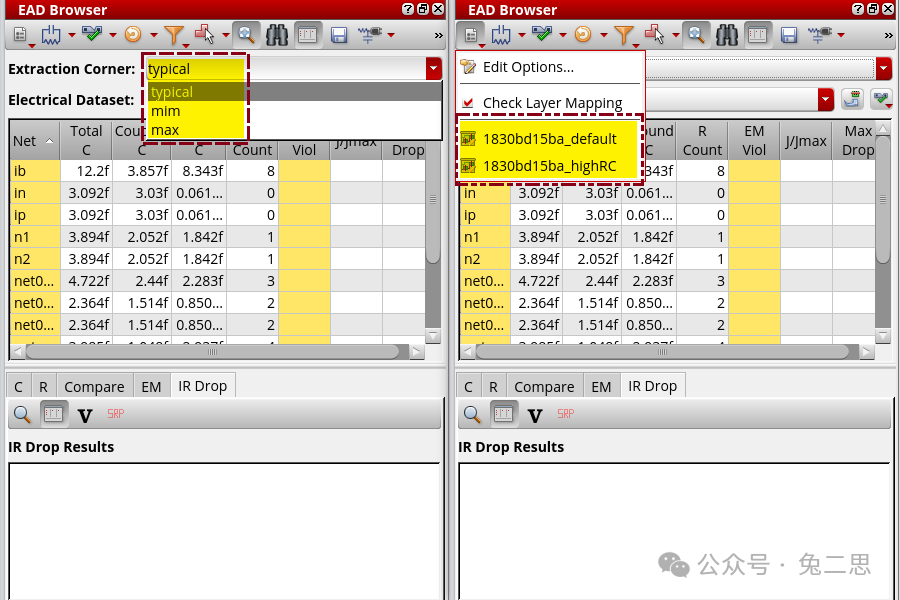

你可以点击下方的「Add」来建立多个 Corners,见下图我创建了typical,min,max这几种常用的工艺角类型。

📌Corner Name 信息会显示在 EAD Browser 面板中。

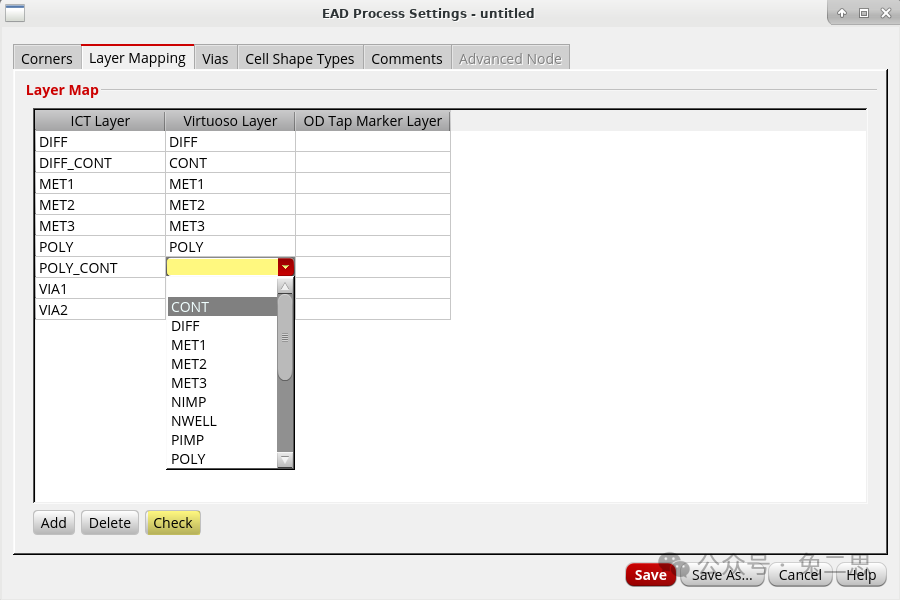

Step 4: 通过 Layer Mapping 子选项卡来指定图层名称。

默认情况下,Layer Map 会把 eadTechfile 和实际 Virtuoso 中所用层名相同的图层自动写入,如果识别到层名不同的情况,需要你手动将图层名称补充完整 —— 双击,输入一个已知的图层名称,或者从下拉菜单中选择一个层次来进行更改。

填好后,点击下方的「Check」可以检查图层的正确性。

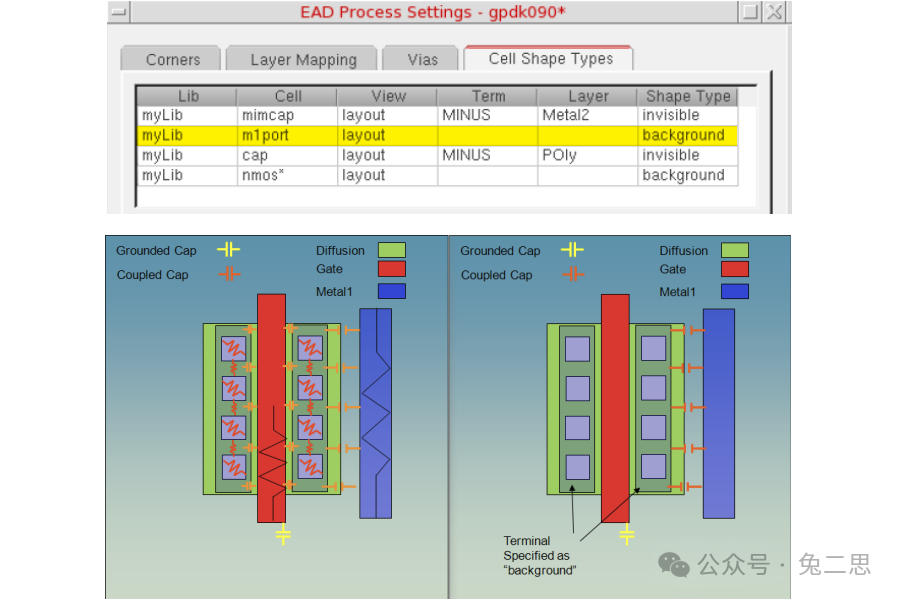

Step 5(可选): 设置提取寄生效应的自定义规则。

Vias 和 Cell Shape Type 两个选项卡,允许我们对通孔和不同的形状类型进行差异化提取,设置后会对 RC 提取和耦合电容的计算产生影响。

下图是官方给的一个应用场景介绍:将 Metal1 定义为背景层,防止在 Pcell 中的 Metal1 形状进行 RC 提取,同时仍然允许计算 Pcell 外部的耦合电容。

Step 6: 点击「Save」把 Process 相关设定保存在.ini文件中,文件默认的保存位置是用户当前工作目录下的 “/.cadence/dfII/EAD/1/process/” 文件夹。

Setup 部分

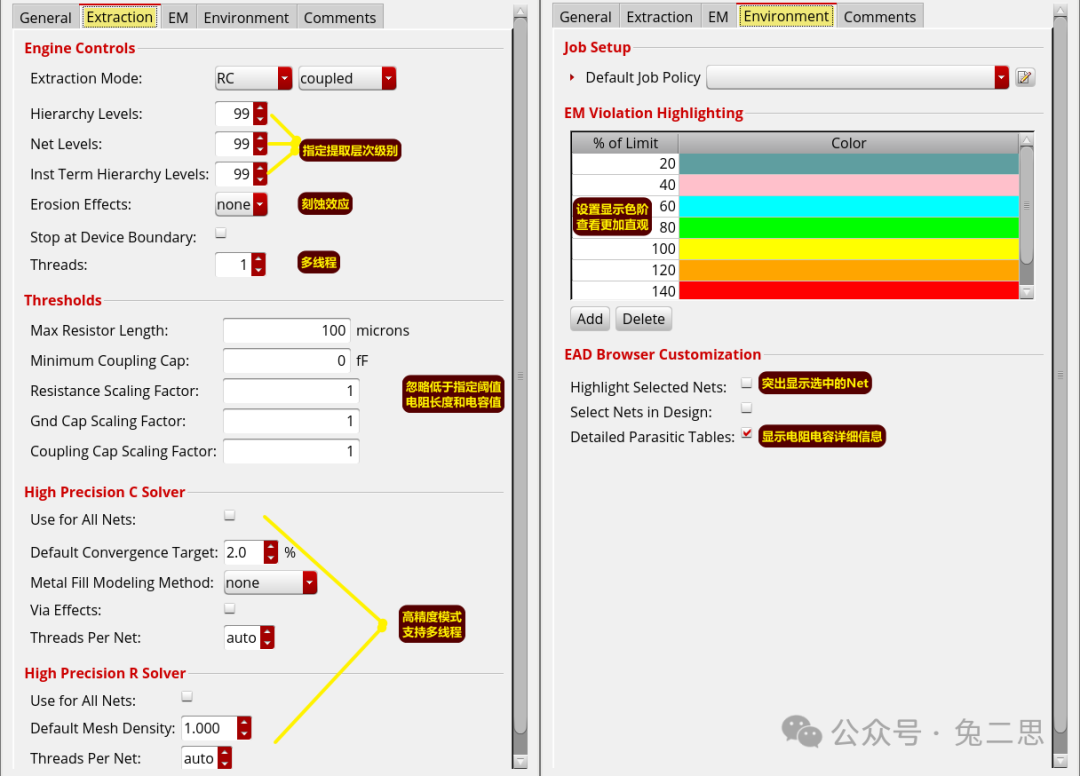

接着来看 EAD Options 选项卡其余的设置内容,挑些常用的参数设置展开讲讲。

1)Extraction Mode

默认是RC提取模式

2)Hierarchy Levels / Net / Inst Term …

指定提取的层次级别,输入「0」仅提取顶层,输入「99」提取所有级别的层次;

3)Erosion Effects

刻蚀效应作用于提取 R/C/RC;

4)Threads

使用多线程模式;

5)Thresholds

提取过程中忽略低于指定阈值的电阻长度,电容值等;

6)High Precision C/R Solver

使用高精度引擎模式,支持多线程,运行比较耗时可以只提取关键信号线;

7)EM Violation Highlighting

设置不同违例范围的显示颜色;

…

其他的也不展开了,自己尝试摸索看看吧~

Step 7: 在选项卡下方输入 Setup Name,点击「Save to」将设置保存在.ini文件中,文件默认的保存位置是用户当前工作目录下的 “/.cadence/dfII/EAD/1/setup/” 文件夹。

不同的设置内容可以保存成多份 ini 配置文件,方便后期使用。

Step 8: 以上设置完成后,返回 EAD Browser 面板,点击图标「Extract Parasitics For All Nets」开始寄生提取(⚠️当前设计窗口要处于编辑状态)。

👇可以看到,Extraction Corner 这里显示了先前设置的 Corner Name 信息,点击下拉列表可以选取其它的工艺角。保存后的 Setup.ini 也会出现在 Options 的下拉列表中。

写在最后

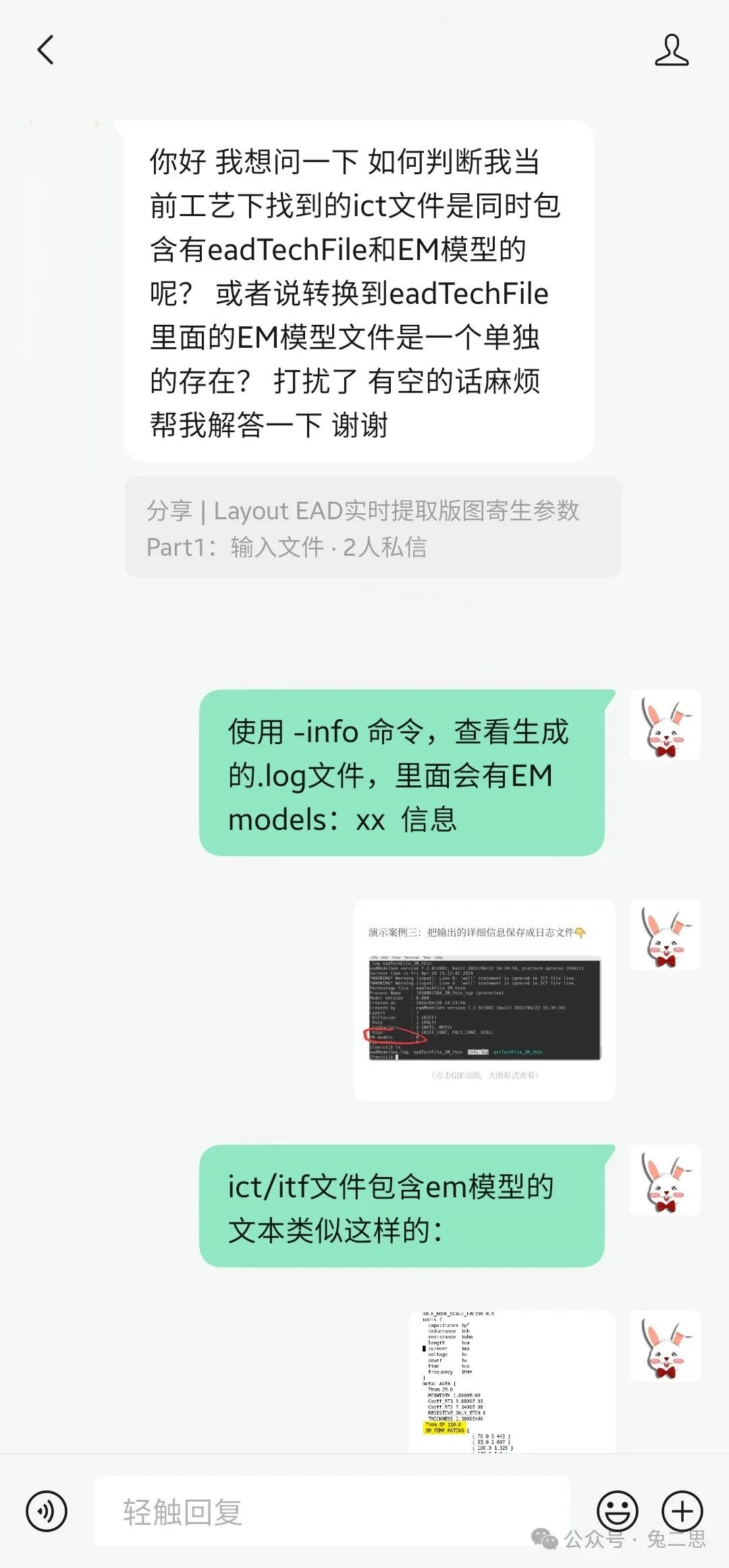

最近后台收到了很多小伙伴的私信,亲切的称呼我“兔哥”,“兔子兄弟”,还有的鼓励我“加班加点”的催更消息。我都有收到哈,会继续努力更文的!

最后附上一个粉丝的答疑,也是对上篇文章做的一点补充:

下篇内容,介绍使用 EAD 工具的一些具体应用场景。

-END-

相关阅读

Layout EAD 实时提取版图寄生参数Part1:输入文件

点击

阅读原文

,参与互动交流